处理器近阈值电压技术解析

什么?还以为只有采用ARM架构设计的处理器才是低功耗的代表?你的知识落伍啦,一颗只需要太阳光就能启动、运行的x86处理器已经问世,其功耗低甚至可以降低到2mW。它是如何减少功耗的?在性能上可能会有何种表现?接下来,本文就将为读者们讲解实现这一奇迹的“秘密武器”——处理器近阈值电压技术的简单原理与优缺点。

如果要评选超大规模集成电路设计的头号障碍,功耗因素的制约一定是强有力的候选人。从宏观角度上看,据美国EPA 2006年的数据,提供I T产业基础支撑的数据中心与服务器消耗了610亿千瓦的能源,这意味着至少数十亿美元的巨额开销,减少功耗势在必行。从微观角度上看,在现今100nm以下的工艺基础上设计制造集成电路,如果仅仅关注速度而不对功耗加以节制,这颗芯片的发热量将会高得根本无法冷却。这就是芯片设计领域里无法回避的“功耗墙”(Power Wall)问题。

在2001年的国际固态电子电路会议上,专家们曾指出当时处理器的功耗正在以指数级速度增长。如果按照这个趋势继续发展而不加以任何节制,则到2005年时高速微处理器的功耗密度将媲美核能反应堆,2010年时将与火箭发动机喷口不相上下,2015年时甚至可以与太阳表面并驾齐驱,如图1所示。所幸,工程师们在降低功耗上的持续努力遏制了这一灾难性趋势。无数富有创造力的低功耗架构、算法、电路与器件在这十几年间被提出和试验,近阈值电压技术便是其中一员。

图1:2001年对“功耗墙”的悲观预测,专家曾预计2015年处理器的功耗密度将与太阳表面并驾齐驱。

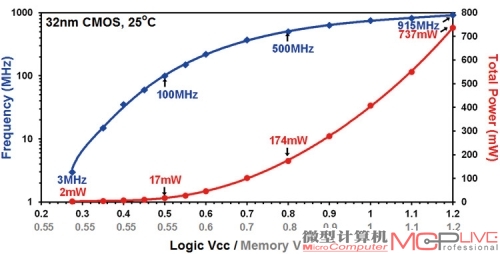

图2:供电电压对晶体管开关延迟与功耗的影响,上图的纵轴为每次操作产生的功耗,下图的纵轴为对数坐标的延迟。上下两图的横轴都是供电电压。两道黑色虚线将本图分成三个区域,从左到右依次为亚阈值、近阈值、超阈值。

大幅降低功耗的关键 处理器阈值电压

为了正确了解近阈值技术的实质,我们需要简单介绍一下现代集成电路当中所广泛使用的MOS管。按照长沟道模型理论的描述,MOS管可以被简单地看成一个开关,施加在栅极上的电压能够控制源极与漏极之间的导电沟道。当栅极电压超过一个特定值时,就可以认为这个MOS管被开启,导电沟道成形,源漏极就被打通了。电子可以在这条源漏极之间的导电沟道上流动从而产生电流,信号得以传递。这个划分开与关界限的“特定值”就是晶体管的阈值电压。所谓的近阈值,就是让MOS管在供电电压紧贴阈值电压的条件下工作,这会对晶体管的性能功耗表现有着极大的影响。

MOS管在0(截止)与1(导通)之间来回切换状态时,会产生动态功耗。这个功耗与供电电压的平方、电路的活跃程度成正比,也就是说,供电电压提高一点,动态功耗都会提高很多,而且电路越活跃,状态翻转越频繁,动态功耗也会相应增加。除了动态功耗外,静态功耗也不容忽视。即便是在截止状态的MOS管,也存在着漏电,特别是对于现在尺寸极小的MOS管来说。原本起到绝缘作用的氧化层厚度已经只有几个原子大小,电子甚至能够凭借量子力学中阐述的隧穿效应越过它,形成漏电流。幸运的是提高晶体管阈值电压或供电电压都可以遏制漏电流的规模,不幸的是提高供电电压亦将提升动态功耗的值。若是保持供电电压不变而只提高阈值电压,则在阈值电压越来越贴紧供电电压的过程中,导电沟道里的电流强度会越来越低。就像让一个能提起100公斤重物的人去提50~90公斤的东西,他的速度会越来越慢一样。晶体管切换状态的本质是依靠导电沟道里的电流来驱动负载,这个电流越小,驱动能力也就越弱,晶体管开关速度就会受到负面影响,损失性能。这是一个不得不做的痛苦权衡。性能和功耗该如何取舍?

从图2我们可以看到,当供电电压超过阈值电压很多时,晶体管就会工作在被称为“超阈值”的状态下。在这个状态下的动态功耗很高,每次切换状态都要消耗不少能量,好处是晶体管处于截止状态时漏电流较少,静态功耗低。高性能微处理器的电压往往都选择工作在这个区域里,因为这个状态下的晶体管能以比较快的速度切换状态。

假设阈值电压不变,如果逐步削减供电电压,那么静态功耗会以缓慢速度抬高,动态功耗会以较快的速度下降,同时下降的还有晶体管的开关速度。当供电电压被削减至阈值电压附近时,仅比阈值电压略高或者略低的时候,就来到了近阈值区域。近阈值理论认为,工作在这个状态下的晶体管可以以延迟提高十倍的代价来换取十分之一的功耗。

若是继续削减供电电压,那么供电电压就会显著低于阈值电压,进入亚阈值区域后晶体管的状态会变得极不稳定。较低的供电电压虽然也能够在导电沟道形成电流,但是电流强度会随着供电电压的持续下降以指数级的速度下滑,差的情况下它的延迟将会提高500倍之多。而且因为供电电压降得太低,虽然动态功耗被控制住了,但是静态功耗又会以近乎指数级的速度上升。因此总功耗只能够下降至超阈值区域的二十分之一,也就是近阈值区域的二分之一。为了多降低一倍功耗付出了五十倍的性能代价,亚阈值区域不是一个明智的选择,学术界与工业界的目光就自然地聚焦到了近阈值区域上。

图3:近阈值区域有极大的性能波动。横轴为归一化处理的频率,纵轴为芯片的频率分布情况。可以看到,在1.2V的电压下,频率分布非常集中,频率变动超过正负18%的芯片极少,但是当供电电压降低到320mV时,整个频率的分布域就变得很大。

图4:阈值电压对失效率的影响。横轴为供电电压,纵轴是失效率,黑色线为90nm工艺,红色线为65nm工艺。可以看到当供电电压逼近阈值电压时,失效率有着数量级上的变化。

图5:供电电压与频率、功耗的关系。横轴第一行数字是核心逻辑供电电压,第二行是缓存电压,左纵轴是处理器所能达到的运行频率,右纵轴是功耗。

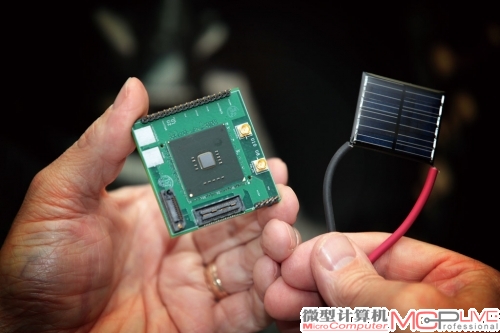

图6:IDF展会上展示的Cla remont处理器,其指令与数据缓存、微指令只读存储器被归类为存储器一类,独立供电,逻辑核心部分包括总线使用另一路供电,两个供电域之间以电平转换器相连。

图7:Claremont处理器使用太阳能电池工作,因此只需要光线照射电池板,处理器就可正常运行。

并不容易 近阈值电压计算面临的困难

相对于亚阈值区域的性能暴降500倍,近阈值区域的表现勉强可以被接受。牺牲九成性能的同时也砍掉了九成的功耗,似乎是一个平手买卖,但是近阈值区域要面临的问题远不止一个性能问题那样简单。

首先,供电电压的削减会对芯片的微架构产生冲击。从微架构的视角看,一颗芯片的晶体管大体可以分成两个部分,一部分是核心逻辑,主要用来进行计算,另一部分是多级缓存体系,主要用来存放指令和数据。这两种晶体管的运行状况完全不同,核心逻辑部分的晶体管经常切换状态,因此以动态功耗为主。而现在的缓存基本以分块分区的模式访问,未被访问的大部分缓存晶体管处于闲置状态,因此以静态功耗为主。要应对这两种截然不同的模式,有学者主张将核心与缓存分开供电。缓存为了削减静态功耗可以使用高阈值型晶体管,核心逻辑部分为了削减动态功耗可以使用低阈值型晶体管。这个解决方法产生了一种新颖的微架构:高阈值、高供电电压的缓存速度快,低阈值、低供电电压的核心逻辑速度慢,于是出现了存储器读写速度超过计算速度的情况!同时,在这个新的微架构下如何重新组织缓存、共享内存,如何搭建多核心并行处理系统都需要重新进行研究。

除了架构上的变形,芯片工作的稳定性也成问题。随着供电电压逐渐缩小、紧贴阈值电压,晶体管的性能波动问题也越来越严重。在每一块超大规模集成电路上保持工作频率都处于同一水准是不可能的任务,对于超阈值区域,工作频率的波动是可控的。但是到了近阈值区域,MOS管的导电沟道电流受到阈值电压、供电电压、温度影响的程度近乎指数级,使得性能上的不确定性大大增加,如图3所示。连专注于研究近阈值计算的学者也不得不承认,这过大的性能波动吓退了大多数对近阈值计算抱有期望的人。

更为糟糕的问题是功能上的完全失效。近阈值区域的晶体管对各种变量更加敏感,使得它缺少容错能力,如图4所示。举例来说,45nm工艺制造的缓存单元在通常电压下失效的概率只有一百万分之一。而在500mV的近阈值区域,失效率骤升5个数量级达到了4%,使得缓存阵列的几乎每一行都会出错。如此高的出错率使得传统的冗余单元根本就无法满足需求。这几项挑战,每一个都不好应付,那么作为处理器巨头的Intel是怎么做的呢?

低功耗仅2mW 神奇的Claremont处理器

Intel很清楚地意识到近阈值电压是一把双刃剑,虽然近阈值技术的代价很大,但是他们认为降低十倍功耗的收获也是值得付出的。为此Intel做了许多研究分析,试图维持近阈值电压稳定运行,并推出了目前为止近阈值技术应用为彻底的一款实验性处理器——Claremont。

Claremont处理器基于32nm高K金属栅极+铜互连工艺制造,但是必须指出的是,从微架构的视角上来看,它并不是先前其他媒体广泛报道的奔腾架构。它只能称之为“奔腾同类”而不是真正的P6或者Netburst架构,因为Intel率先引入奔腾pro处理器,并随后成为微处理器标配技术的乱序执行并没有在Claremont上出现。从这个角度上看,Claremont甚至更加像同为顺序执行架构的Atom处理器。乱序执行的引入虽然显著提高了性能,但是也使得设计更为复杂,而且每一条指令除了经过执行步骤,还要经过流水线前端的冒险检测、调度分发,流水线后端的重新排序,这会导致指令执行的平均功耗大大增加,因此我们推论,Intel抛弃乱序执行的考虑应该是避免设计上的过度复杂,以及乱序执行的引入将恶化功耗表现。所以它的终架构是顺序多发射,有分支目标缓冲区与动态分支预测功能,囊括8K B的指令与数据缓存,核心面积为2mm2,约有六百万个晶体管。上文中提到,在近阈值电压的条件下,存储器和核心逻辑所需要的供电电压是不同的,Intel也意识到了这一点,因此Claremont的缓存与核心逻辑是分开供电设计的。

核心逻辑到缓存之间的供电电压不同,意味着信号在这两个区域之间跨越需要引入电平转换器,这会引入额外的延迟。好在根据美国密歇根州立大学研究人员的仿真分析,这个电平转换器引入的延迟相对访存延迟来说可以忽略不计。同时,针对占据核心逻辑面积20%的浮点处理单元,Intel专门设计了一个功耗管理单元,进行功率门控与时钟门控。这两项技术是低功耗设计当中的必备武器,我们先来解释一下时钟门控。整颗处理器都依靠时钟信号的协调来运行,因此需要有一个时钟电路网络分布在整个芯片当中.时钟信号的跳变是非常频繁的,因此它的动态功耗很高,在必要的时候应该引入时钟门控,断开时钟信号与闲置模块的连接来削减动态功耗。第二项功率门控技术,就是我们平时说的“睡眠”技术。以Claremont的浮点功耗控制为例,当处理器前端检测到没有浮点指令发射进入流水线的时候,就可以使用功率门控电路来切断浮点单元的供电电压,以此避免白白浪费的漏电流,并且将这块失去供电的浮点单元的输出做隔离处理,防止它的状态影响到后级电路。

为了保持近阈值电路的稳定工作,Intel团队还将自己使用的电路单元库进行了筛选。有四个或者更多晶体管堆叠相连的、带有宽传输门的多路复用器、扇入数目大于四的单元都被筛除。因为稳定性仿真分析表明它们会恶化延迟衰退问题,晶体管的宽度小于工艺准许小宽度两倍的也被筛除,因为它们的延迟波动难以控制。除了这些前期筛查工作,电路上的稳定性优化也是必要的。例如时钟歪斜问题,跨供电域传播时,时钟信号的到达时间有时候并没有踩在预想的节拍上,时钟网络需要仔细调校和排布来应对这个问题。值得一提的是,Intel在Claremont上抛弃了自45nmCore家族处理器上使用的8晶体管结构的缓存单元,而改用10晶体管缓存单元。与其他论文中已经公布的8晶体管结构相比,这种10晶体管的结构在写入能力以及存储稳定性上进行了加强。但是显而易见地,这一举动导致同样大小的缓存将占用更多的面积,这是通过牺牲芯片面积来换取近阈值电压下的稳定执行。一系列的优化工作进行完毕以后,Claremont处理器被证明可以在280mV到1.2V的宽电压范围上运行。

从图5中可见,Claremont处理器的核心部分能够工作在低280mV的超低电压下(睡眠模式的电压可以进一步减少至10mV),缓存部分则使用550mV的独立供电。在这个供电水平上处理器能够稳定运行在3MHz,功耗仅为2毫瓦,当核心逻辑与缓存的电压同时提高至1.2V的大值时,功耗也仅为737毫瓦,可以说它满足了极为苛刻的功耗要求。

可惜的是,尽管Intel在自己的ISSCC论文中详细分析了这块芯片的功耗表现,并确认使用近阈值技术会导致性能衰减,但是对性能衰减的幅度并没有量化分析。因此我们并不清楚Claremont在降低绝对功耗的追求上,牺牲了多少性能。但可以肯定,损失一定不低。

暂不明朗 近阈值电压计算前景浅析

尽管近阈值技术的实际样品已经诞生,移动设备的续航时间有望得到大幅提高,然而一些业内厂商却并不看好。高通旗下的研究人员在近期就发表了一篇仅为三页的会议论文,唱衰近阈值计算的前景。论文摘要中便声称许多先进低功耗技术都牺牲了性能、电路质量与面积,并点名说近阈值电压就是一个好例子,该技术的应用前景并不广阔。他们认为虽然近阈值核心也可以采用并行架构的设计思路来弥补性能不足,但这会提升嵌入式设备的成本。而选用10晶体管的缓存单元将进一步把芯片面积抬高20%~40%。总体来看,近阈值电压的使用牵涉到架构、电路、器件工艺多个层面的取舍,涉及到众多因素,高通公司的论文的确点中了近阈值技术的软肋。市场会在电池续航力时间与流畅计算体验之间倾向哪一边?请让我们拭目以待。