解析CES 2013上的移动处理器(中)

上期我们为大家详细介绍了NVIDIA Tegra 4,包括Tegra 4的设计、Cortex-A15的性能以及GPU的表现。作为全球首款四核Cortex-A15处理器,Tegra 4受到玩家的关注理所应当。不过ARM移动处理器市场并非只有NVIDIA,三星即将推出的采用big.LITTLE技术的Cortex-A15搭配Cortex-A7的“混合处理器”Exynos 5 Octa也是展会中的亮点。本期我们将重点介绍它的情况。

大big,小LITTLE——ARM的功耗控制技术

ARM处理器发展到今天,随着性能的上升、晶体管数量的增多,功耗控制日渐困难,制程工艺也由于受到材料物理极限的限制,很难快速进步。在工艺很难控制功耗的情况下,厂商不得不另辟蹊径,在产品结构设计上进行优化。之前在Cortex-A9四核心处理器上,NVIDIA率先采用了“4+1”技术,用四个“正常”的高性能核心搭配一个低负载、低电压、低频率核心来平衡性能和功耗,并将这项技术延续到采用Cortex-A15的四核心处理器Tegra 4上。与此类似的是,ARM也打算通过改进架构设计来降低ARM处理器在整个使用寿命中的平均功耗。在CES 2013上,ARM带来的是传说已久的big.LITTLE技术,主要产品的展示则交由三星完成,具体产品型号是Exynos 5 Octa。

big.LITTLE的设计思想

从CPU的发展角度来看,类似于big.LITTLE这样的设计思想,并不是突然出现的。此类思想设计早来自于硅谷的一家CPU设计公司Montalvo Systems——这家公司在2009年就被SUN纳入囊中。在Montalvo Systems公司的设想中,他们的x86处理器将会用高性能、大型CPU核心搭配低性能、低功耗的小核心产品,在功耗和性能上将会“左右逢源”,是未来处理器发展的重要方向。在Montalvo Systems被SUN收购后,SUN又被甲骨文收购,一波三折的经历使得Montalvo Systems烟消云散,其设计也渐渐无人提及。

除了Monta lvo Systems外,英特尔也在关注类似技术。它曾经以“Scheduling Heterogeneous Multi-Cores through Performance Impact Estimation(PIE)”为题目,研究方向是异种多核处理器的内部调度以及性能表现。其中异种多核就是指高性能的大处理器和低功耗的小处理器之间的调配问题。

花开了这么多年,终的果子还是让ARM先尝到了。ARM在Cortex-A15架构发布后不久,就逐步公开了其对异种多核处理器的研究计划,并给予这种技术一个特殊的名字——big.LITTLE。其中代表大核心的“big”使用小写,代表小核心的“LITTLE”使用大写,在技术命名上颇下了一番工夫,从名称就可以感觉到,ARM对其中包含的低功耗小核心“LITTLE”更为看重。

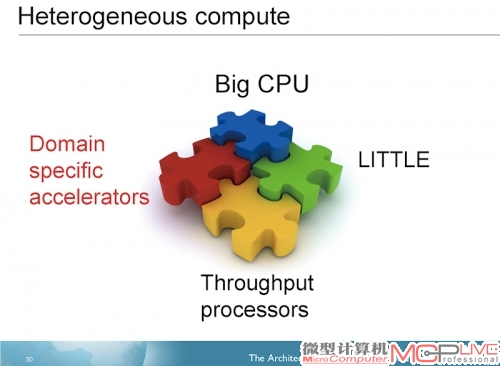

ARM期盼的不仅仅是不同CPU之间的搭配,它还希望将不同架构的处理器统一起来为系统提供能量。

实际上ARM所考虑的异种多核处理器并非都是CPU的搭配。在ARM的介绍中,异种计算(Heterogeneous Compute)包含的处理器包括big CPU、LITTLE CPU、Domain specific accelerators(加速处理器,各种特殊的专用单元模块)以及Throughput processors(生产处理器,主要是指GPU)四大部分,这四个部分在未来的计算中会根据软件需要进行计算调配,在合适的地方发挥自己强的性能。

ARM自己也在做一些实验。根据ARM方面的消息,ARM开发了一款实验芯片,使用了3个Cortex-A7核心和2个Cortex-A15核心组建big.LITTLE架构的CPU(这颗实验CPU没有涉及GPU部分)。这颗芯片主要用于验证big.LITTLE的功耗、性能、软件以及内部结构设计等问题。需要注意的是,虽然在ARM自己的实验中,big核心和LITTLE核心的数量并不对等,但是ARM在建议设计阶段要求设计人员使用完全对等的big和LITTLE核心,也就是1个big核心必须对应一个LITTLE核心,这样才能做到有效率、快速的任务迁移。在三星即将推出的Exynos 5 Octa上,4个Cortex-A15核心就恰好对应了4个Cortex-A7的核心。

目前的big.LITTLE技术只是ARM设想中的第一代,第二代big.LITTLE技术在进一步优化内部程序切换和进一步控制功耗的同时,CPU核心也会换成Cortex-A57( big核心)搭配Cor tex-A53(LITTLE核心),全新的ARMv8 Cortex-A50架构家族将会支持64bit计算,性能会有更为明显的提升。

大小随心切换——big.LITTLE技术内幕

big.LITTLE技术的主要目的是在需要高性能的时候使用big核心,对性能要求较低的时候使用LITTLE核心。这两句话说起来简单,但是做起来可没这么容易。根据ARM官方资料,为了保证big.LITTLE技术的有效性,big.LITTLE技术需要在CPU内部的硬件设计上做出如下设计:

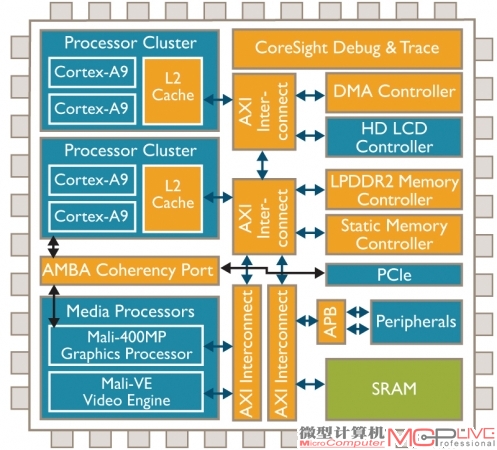

●CoreLink AMBA片上互联系统

ARM设计的片上互联系统主要作用是提供各个端口和处理器之间的互联总线,其中包括ARM核心和Mali GPU以及big.LITTLE技术所需要的不同异构CPU核心之间的连接。这种互联设计主要是单向通道架构(使得数据传输线路所需要的设计更为简单),可以支持多个未完成的事物(可以执行并行传输,可以同时兼顾高性能和低功耗),地址和数据通道都是独立的(降低传输延迟、提高传输频率),灵活性也很出色(使用对称的主接口和辅助接口,可以灵活方便地应用点到点系统)。

●CoreLink CCI-400 高速缓存一致性互连

缓存一致性是big.LITTLE特别重要的一部分。由于big.LITTLE技术需要在完全不同的异构CPU之间传递数据,因此缓存本身就需要通过一致性来保证任务切换的快速流畅。CoreLink CCI-400本身可以支持不少的功能,比如一致性的软件管理和硬件管理,可以确保数据在传输过程中得到快速刷新和更改,能够减少外部内存的访问等。这些技术的综合使用可以在big.LITTLE架构中充分保证数据本身的安全和稳定。

●AMBA中断控制器

用于向中断系统提供各种接口,并且能够缩短中断延迟。在big.LITTLE中,来回切换大量任务需要强大的中断控制器进行管理,AMBA恰好可以提供类似的功能。

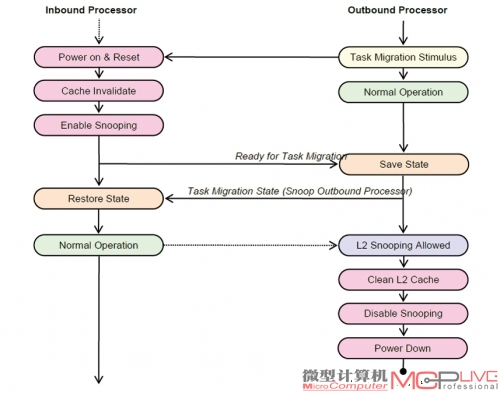

除了这些硬件技术外,以三星目前公布的处理器为例,big.LITTLE技术添加了4个新的Cortex-A7核心,这4个核心在内部结构上和原有的4个高性能核心是基本独立的,4个LITTLE核心拥有自己的L2缓存,并不和big核心共享缓存数据。这就意味着big.LITTLE在任务切换时需要先转移数据并唤醒沉睡的目标CPU。根据ARM的说明,在任务切换时,系统会将源核心的数据和状态(包括CPU架构状态和缓存数据)全部写入外部存储器(一般是内存)中,目标核心会从内存中读取这些数据然后准备工作。

ARM设计了号称“无缝切换”的技术,来保证CPU在big和LITTLE核心之间切换时,不会让用户感受到延迟。

由于这个切换存在时间,因此不但用户可能感觉到不流畅,而且还可能影响到系统的性能表现。在这个问题上,ARM设计了号称“无缝切换”的技术。在这个技术中,CPU被加入了一个称为“snoop”监听的功能。在数据转移过程中,监听功能可以让目标处理器获得源处理器的详细信息,从而大幅度降低了需要预加载L2缓存而带来的延迟,并使得整个系统可以更为快速地完成切换。根据三星的数据,存取数据的时间和CPU频率成反比,在1GHz时,单次存或者取数据的延迟仅为5.0μs,2GHz时只有2.5μs。根据三星估计,一般应用切换时间应该控制在20μs以内。如此低的延迟基本上可以算作无缝切换,用户不会看到明显的卡顿,可以说全程基本保持流畅。

从早期的CPU簇切换到现在的自由切换,big.LITTLE的发展也经历了。

在CPU切换的功能性设计上,早期的设计是big CPU和LITTLE CPU打包后,以“簇”的方式运行。换句话来说,如果是4个big CPU和4个LITTLE CPU,那么切换只能“4对4”,不能出现某2个LITTLE CPU切换至某2个big CPU,这是不允许的。不过这样的设计明显缺乏灵活性,并且很难有效降低功耗。在新的设计中,“簇”被取消,CPU之间的绑定也不复存在。新的CPU migration切换模式将一个big CPU和一个LITTLE CPU绑定为一组,在切换时可以在一个big-LITTLE CPU组中进行切换。不需要切换的核心则保持沉睡或者继续执行计算任务。这样的设计方式大大提升了big.LITTLE技术的意义,并使得big.LITTLE切换时的灵活性更高,更有效率。

在软件支持上,当前的big.LITTLE技术已经在操作系统中得以支持,因此系统方面问题不大。软件方面则需要为big.LITTLE做出一些改变,才能更好地配合系统进行切换,这就需要软件开发商针对big.LITTLE进行一些优化了。此外,目前的big.LITTLE切换是一对一的切换,ARM还在研究big.LITTLE MP技术。这项技术干脆将不同的big CPU和LITTLE CPU放在一个篮子里,让操作系统根据应用需求自动处理需要执行任务的CPU核心。比如较重的计算任务给big核心,较轻的给LITTLE核心,达到负载和能耗之间的完美平衡。这些处理需要操作系统层面更多的支持,因此短时间内还看不到任何希望。

big.LITTLE技术的节能效果如何?

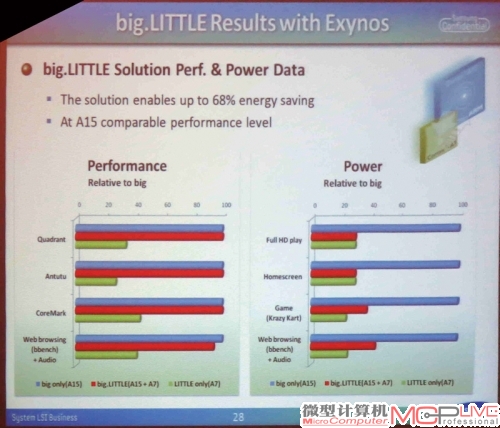

big.LITTLE的主要设计目的是节能,那么这种技术的节能表现究竟如何呢?目前对big.LITTLE有深入研究的厂商暂时只有三星一家。在之前举行的一次ARM技术会议上,三星公布了一些在使用big.LITTLE技术后,处理器在性能方面的数据。根据这些已曝光的资料,我们可以窥得big.LITTLE技术终体现在性能和功耗上的效果。

三星所做的实验首先给出了一套配置。CPU方面是4个Cortex-A15核心搭配4个Cortex-A7核心:前者的频率范围是1.7GHz~0.8GHz、电压是1.2V~0.9V;后者的频率范围是1GHz~0.2GHz、电压也是1.2V~0.9V。内存方面配备了800MHz的LPDDR3内存,系统是Android ICS系统,kernel版本是3.4。

除此之外,三星还特别说明了big.LITTLE核心切换的上下限,具体内容如下:

●big核心向LITTLE核心切换

当Cortex-A15的核心运行频率达到800MHz 100ms、且CPU占用率小于70%的时候,会切换到Cortex-A7核心。

●LITTLE核心向big核心切换

当Cortex-A7的核心频率达到1GHz 100ms、且CPU占用率大于或者等于95%时,会自动切换到Cortex-A15核心。

三星没有说明这样设定的原因。但是我们可以用不算严谨的算法估算一下,Cortex-A7的理论性能大约是1.9DMIPS/MHz,Cortex-A15大约是3.5DMIPS/MHz。Cortex-A15在800MHz、70%的CPU占用率时,简单估算可得其此时的性能输出大约是1960MIPS。Cortex-A7在1GHz、95%的CPU占用率时,简单估算可得其性能输出约为1800MIPS。两者数据非常接近。可以简单地认为三星设定的这个切换点,恰好是Cortex-A15和Cortex-A7架构性能相当的一个点,在这个点上切换不会造成明显的性能落差,能更有效地保证性能过度的平衡和稳定。

至于实际性能和节能效果,三星也给出了一些数据。三星对比了仅仅使用Cortex-A15、big.LITTLE搭配状态以及仅仅使用Cortex-A7状态下的功耗和性能测试成绩。从终的测试结果我们可以看出,在性能方面,红色横条代表的big.LITTLE在性能方面和蓝色的纯Cor tex-A15性能相当,部分测试有小幅度的性能损失,都很轻微。但是在功耗方面,big.LITTLE技术在诸如高清播放、屏幕主界面时的功耗和仅使用Cortex-A7处理器是完全一样的( 因为此时Cortex-A15已经被关闭)。只有在网页浏览和游戏中,由于部分时间需要启动Cortex-A15核心,因此big.LITTLE功耗表现会明显高于只使用Cortex-A7处理器时。三星表示,相比4个纯粹的Cortex-A15核心,big.LITTLE技术会节省多68%的电能。

采用big.LITTLE技术的Cortex-A15搭配Cortex-A7的“混合处理器”——三星Exynos 5Octa的介绍就到这里结束了。在下一期的文章中,我们将继续带来CES 2013上所发布新产品的更多精彩技术分析。文章中将包括国产Cortex-A7处理器、高通Krait 300、Krait 400架构以及英特尔新凌动处理器Z2580等诸多内容。我们下期再见!